AMD Strix Halo 处理器芯片创新亮相:全新互联设计,3D 缓存接口再进化

开启处理器芯片新篇章:AMD Strix Halo 引领互联革命,3D 缓存接口再升级

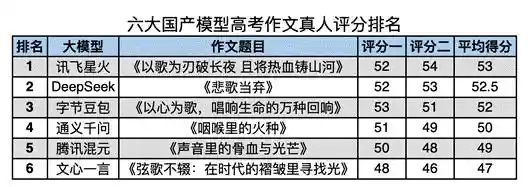

2月19日消息,华硕电脑有限公司中国区总经理俞元麟在B站账号“普普通通Tony大叔”昨日分享了两位B站UP主万扯淡和kurnal共同制作的关于AMD锐龙AIMax395"StrixHalo"处理器芯片的结构分析视频。

AMD在锐龙AIMax395上采用了两颗4nm制程的CCD芯片(每颗面积为67.07平方毫米)和一颗同样由台积电4nm工艺制造的IOD芯片(面积为307.584平方毫米)。这款处理器的IOD芯片内部集成了一个拥有20个计算单元的超大规模核显。 AMD此次在锐龙AIMax395上的设计展示出了其在芯片制造技术方面的卓越进步。通过采用先进的4nm制程技术,AMD不仅提高了处理器的性能,还进一步优化了功耗与散热管理。尤其是集成的超大规模核显,对于那些不需要独立显卡的用户来说,是一个非常吸引人的亮点。这表明AMD正在不断努力,以满足市场对高性能和低能耗产品的需求。

在CCD部分,AMD 大体上沿用了桌面端锐龙 9000“Granite Ridge”处理器的 CCD 核心区域 IP 设计,因此“Strix Halo”芯片也保留了用于 3D V-Cache 集成的 TSV 接口引脚。 这种设计策略表明,AMD 在开发新的服务器芯片时,仍然在一定程度上依赖于其成熟的桌面端产品线。这不仅有助于降低研发成本和时间,还可能意味着“Strix Halo”芯片将继承桌面端产品的某些优势,如更高的性能和更好的能效。然而,这也引发了一些关于 AMD 是否能够充分发挥服务器市场独特需求的疑问。毕竟,服务器环境对稳定性和可扩展性的要求与桌面环境存在显著差异。

不过,AMD对CCD的边缘I/O进行了改进,将基于SerDes的互联方式改为了水平扇出封装技术。“StrixHalo”所采用的CCD在纵向上的长度减少了0.34毫米,互联区域的面积缩减了42.3%。

在IOD部分,中间区域自然是由两个簇组成的大型RDNA3.5核显,而其两侧稍外的部分则是两块16MiB的MALL Cache。边缘位置则分布着8组共计256位宽的DRAM内存接口。 这种设计不仅增强了处理器的图形处理能力,还显著提升了系统的缓存性能和内存带宽。这样的配置对于游戏和高性能计算来说尤其有利,能够提供更流畅的游戏体验和更高的数据处理速度。此外,IOD的设计优化也意味着系统能效比得到了提升,这对于追求高性能同时又注重能耗比的用户来说是一个非常吸引人的特点。

"Strix Halo" IOD 下方则分布了 NPU、媒体引擎、PCIe 接口在内的一系列其它电路。

电脑硬件最新资讯

2025-06-09 04:10:47

2025-06-09 03:34:23

2025-06-09 01:45:37

2025-06-09 01:36:41

2025-06-08 23:58:39

2025-06-08 23:50:57

2025-06-08 23:49:17

2025-06-08 23:46:43

2025-06-08 23:46:08

![[岚图FREE+]六款车漆惊艳亮相,本月预售点燃市场热潮](./glo_kj_images_min/27.png)

2025-06-08 23:44:20

2025-06-08 23:43:52

2025-06-08 23:43:42

2025-06-08 23:36:22

2025-06-08 23:35:07

2025-06-08 23:34:02

2025-06-08 23:33:58

![[曙光AI基础设施:为智能时代全栈赋能!]](./www_images/20256/202568/image_20250608233146368639.webp)

2025-06-08 23:31:51

2025-06-08 23:30:00

2025-06-08 23:28:56

2025-06-08 23:28:52

2025-06-08 23:24:16

2025-06-08 23:22:05

2025-06-08 23:21:36

2025-06-08 23:19:54