发布日期:2025-02-21 12:04:51

突破极限:铠侠革新闪存技术,332层存储缔造全球第一容量与速度传奇

332层存储革命:铠侠引领闪存新时代,重塑容量与速度巅峰

2月21日,铠侠宣布与闪迪合作研发的第10代BiCS3D NAND闪存取得了重大突破。这种新型闪存在堆叠层数、存储密度以及接口速率方面均实现了显著提升,标志着在存储技术领域迈出了重要的一步。 这种技术创新不仅展示了铠侠和闪迪在研发领域的强劲实力,同时也预示着未来存储设备将拥有更高的性能和更大的容量。对于消费者而言,这意味着未来的电子设备可能会提供更快的数据读写速度和更可靠的存储解决方案。此外,这一进步也有望降低单位存储成本,为市场带来更具竞争力的产品。

铠侠新推出的闪存采用了CBA双晶圆键合技术,分别制造CMOS控制电路和NAND存储阵列,之后再将它们键合在一起。这一技术实际上借鉴了长江存储的Xtacking晶栈架构。

3D堆叠层数达到了前所未有的332层,相比第8代的218层增加了约38%,同时也超越了SK海力士的321层、三星的290层、美光的276层以及西数的218层。

铠侠的目标,是在2027年造出1000层堆叠的3D闪存。

由于增加了更多的层数,存储密度据称提高了59%,计算下来大约为每平方毫米36.4Gb,这同样远远超过了竞争对手。西部数据只能达到每平方毫米22.9Gb,而SK海力士更是仅有每平方毫米20Gb。

不过,铠侠暂未公布具体的闪存类型(TLC/QLC),以及单Die容量。

新款闪存同样兼容ToggleDDR6.0接口标准,其传输速率高达4800MT/s,较上一代提升了33%,再次创下新高,超越了美光和西数的3600MT/s。

此外,铠侠此次还引入了PI-LTT低功耗技术,使输入功耗降低了10%,输出功耗减少了34%,从而更符合AI技术的需求。

电脑硬件最新资讯

《瘟疫传说》新篇章:《共鸣:遗产觉醒》2026重磅来袭

2025-06-09 04:10:47

《战争机器:事变日》官宣!虚幻引擎5打造未来战争新纪元

2025-06-09 03:34:23

《天外世界2》神秘面纱揭开:全新预告震撼首发!

2025-06-09 01:45:37

《颠覆想象!微软正式发布全新游戏掌机ROG Xbox Ally/X》

2025-06-09 01:36:41

《媒体为何不买Switch 2?编辑自嘲:故事的尽头仍是妥协》

2025-06-08 23:58:39

⚡安克70W急速充电头首发!2C1A旗舰配置+可折叠插脚,搭配USB-C线仅售169!

2025-06-08 23:50:57

音响传奇再升级:宝华韦健鹦鹉螺HiFi落地音箱直降2000元,794300元震撼价来袭!

2025-06-08 23:49:17

《神秘面纱即将揭开:富士 X-E5 真机首曝定档 6 月 12 日发布》

2025-06-08 23:46:43

雷神新款显示器震撼发布:23.8英寸2K 240Hz高刷屏,首发价仅899元!

2025-06-08 23:46:08

![[岚图FREE+]六款车漆惊艳亮相,本月预售点燃市场热潮](./glo_kj_images_min/27.png)

[岚图FREE+]六款车漆惊艳亮相,本月预售点燃市场热潮

2025-06-08 23:44:20

索泰发布电竞界黑科技:F5电竞香水,让你在游戏中闻香制胜!

2025-06-08 23:43:52

蔚来打造川藏线奇迹:318国道换电网络下月底全线贯通

2025-06-08 23:43:42

《GT赛车》选车标准大揭秘:山内一典的私心与热爱

2025-06-08 23:36:22

《从默默无闻到财富巅峰:王宁登顶河南首富,泡泡玛特的奇迹之路》

2025-06-08 23:35:07

《小艺智能解读高考作文:AI互动式深度解析强势登场》

2025-06-08 23:34:02

速度传奇!本田思域TYPE R终极版限量40台惊艳发布

2025-06-08 23:33:58

![[曙光AI基础设施:为智能时代全栈赋能!]](./www_images/20256/202568/image_20250608233146368639.webp)

[曙光AI基础设施:为智能时代全栈赋能!]

2025-06-08 23:31:51

《Jon Peddie:未来五年台式机独立显卡渗透率将飙升至86%》

2025-06-08 23:30:00

九州风神冰域新品首发:自研PWM水泵+2.4英寸方屏, redefine 水冷散热新体验!

2025-06-08 23:28:56

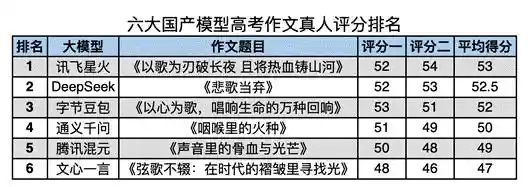

《巅峰对决!六大国产AI模型高考作文表现大揭秘:讯飞星火夺冠》

2025-06-08 23:28:52

氪星科技中国造:机器人4号搭载脉塔智能关节模组革新超人战斗力

2025-06-08 23:24:16

全球领先九连冠:中国抽水蓄能装机容量持续领跑世界

2025-06-08 23:22:05

【里程碑】2024:我国海洋生产总值首破10万亿!

2025-06-08 23:21:36

《频谱飞跃:AMD显卡在1GHz到3GHz区间五次夺冠》

2025-06-08 23:19:54

热血骑士!京东外卖授予三名助考骑手每人3000元特别奖励